作為最重要的設(shè)計(jì)參數(shù)之一,選擇環(huán)路帶寬涉及到抖動(dòng)、相位噪聲、鎖定時(shí)間或雜散之間的平衡。適合抖動(dòng)的最優(yōu)環(huán)路帶寬BWJIT也是數(shù)據(jù)轉(zhuǎn)換器時(shí)鐘等許多時(shí)鐘應(yīng)用的最佳選擇。如果BWJIT并非最佳選擇,首先要做的仍是尋找最優(yōu)環(huán)路帶寬。

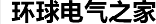

圖1中,鎖相環(huán)(PLL)與壓控振蕩器(VCO)噪聲交叉處的偏移,BWJIT(約為140kHz)通過(guò)減少曲線下方的面積來(lái)優(yōu)化抖動(dòng)。

圖1:最優(yōu)抖動(dòng)帶寬

盡管此帶寬BWJIT對(duì)抖動(dòng)而言是最優(yōu)的,但對(duì)于相位噪聲、鎖定時(shí)間或雜散卻并非如此。表1給出了環(huán)路帶寬對(duì)這些性能指標(biāo)的影響的大致參考。

性能指標(biāo) | 最優(yōu)帶寬 | 備注 |

抖動(dòng) | BWJIT | 最優(yōu)值一般為BWJIT。在低集成限制更高的一些情況下,有時(shí)較窄的環(huán)路帶寬實(shí)際上效果更好。 |

鎖定時(shí)間 | 無(wú)限 | VCO鎖定時(shí)間隨著環(huán)路帶寬的增加而提高,但有時(shí)會(huì)受到VCO校準(zhǔn)時(shí)間(用于集成VCO)的限制,或因VCO輸入電容等寄生電容而使帶寬無(wú)法增加。 |

雜散 | 0Hz | 一般而言環(huán)路帶寬越窄,雜散越好,但有時(shí)會(huì)由環(huán)路濾波器周?chē)鷣?lái)自主板或芯片上的串?dāng)_所主導(dǎo)。 |

相位噪聲 | 0Hz或無(wú)限 | 如果相位噪聲低于最優(yōu)抖動(dòng)帶寬,相位噪聲會(huì)隨著帶寬的變寬而增大,直到變成僅為輸入基準(zhǔn)和PLL造成的噪聲。 如果相位噪聲偏移大于最優(yōu)抖動(dòng)帶寬,相位噪聲會(huì)隨著環(huán)路帶寬的變窄而增大,直到變成僅為獨(dú)立的VCO噪聲。 |

表1:環(huán)路帶寬對(duì)關(guān)鍵參數(shù)的影響

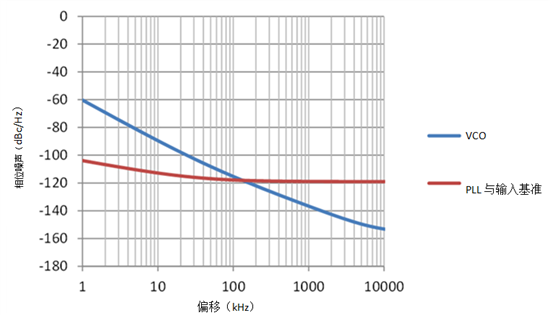

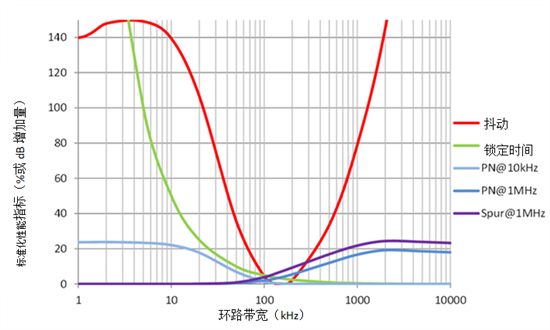

為了說(shuō)明表1,圖2中的模擬顯示了變化的環(huán)路帶寬的影響。鎖定時(shí)間與抖動(dòng)標(biāo)準(zhǔn)化指標(biāo)為圖2中從最小值增加的百分比。雜散與相位噪聲指標(biāo)為圖2中從最小值增加的分貝。

圖 2:環(huán)路帶寬對(duì)標(biāo)準(zhǔn)化性能的影響

如圖1所預(yù)測(cè),環(huán)路帶寬為140kHz左右時(shí),最優(yōu)抖動(dòng)確實(shí)為最佳。環(huán)路帶寬超出此范圍會(huì)有利于鎖定時(shí)間和10kHz相位噪聲,但是會(huì)降低雜散和1MHz偏移的相位噪聲。

因此,選擇環(huán)路帶寬的一種較好的方法是先選擇最優(yōu)抖動(dòng)帶寬(BWJIT),然后增加帶寬提高鎖定時(shí)間或低頻偏相位噪聲,或者降低帶寬提高高頻偏相位噪聲或雜散。

選擇正確的環(huán)路帶寬遇到問(wèn)題?登錄并在下方評(píng)論。

其他信息