當前位置: 首頁 > 工業電子產品 > 其他電子產品 > 開發板,套件,編程器 > 開發板

發布日期:2022-10-14 點擊率:120

前面兩篇文章分享了我對數字基帶信號與成型濾波的理解、測試、驗證,本文將分享DPSK在AD9361上的實現。思路是這樣的,首先在Matlab上驗證DPSK調制后的頻譜,然后在FPGA中采用偽隨機序列作為原始數據,經上采樣、成型濾波后送入AD9361,由AD9361完成IQ調制并最終發射出去。在本文中,最終的已調DPSK信號,其物理層速率是2Mbps,占用帶寬為2.5MHz,物理層與占用帶寬是聯動的關系。

讀入上一篇文章中生成的隨機序列,進行4倍上采樣,然后使用filter函數對上采樣后的序列進行成型濾波(濾波器系數也是在上一篇文章中生產的),成型濾波后輸出的數據與載波相乘得到 DPSK調制信號,最后繪制DPSK已調信號的頻譜。Matlab代碼如下:

clear;clc;

ps=1*10^6; %碼速率為1MHz

Fs=4*10^6; %采樣速率為4MHz

fc=1*10^6; %載波頻率為1MHz

N=20000; %仿真數據的長度

coe_int=importdata('D:Tempmatlabcoe_int.txt');

s=importdata('D:Tempmatlab and_data.txt');

t=0:1/Fs:(N*Fs/ps-1)/Fs; %產生長度為N,頻率為fs的時間序列

%以Fs頻率采樣

Ads=upsample(s',Fs/ps);

rcos_Ads=filter(coe_int,1,Ads);

%產生載頻信號

f0=sin(2*pi*fc*t);

%產生DPSK已調信號

dpsk=rcos_Ads.*f0;

%繪制成形濾波后信號頻譜、DPSK信號頻譜、DPSK信號時域波形

m_dpsk=20*log10(abs(fft(dpsk,1024)));

m_dpsk=m_dpsk-max(m_dpsk);

%m_dpsk=mean(m_dpsk,1);

%設置幅頻響應的橫坐標單位為MHz

x_f=[0:(Fs/length(m_dpsk)):Fs/2];x_f=x_f/10^6;

%只顯示正頻率部分的幅頻響應

mdpsk=m_dpsk(1:length(x_f));

plot(x_f,mdpsk);

legend('DPSK已調信號頻譜');

xlabel('頻率(MHz)');ylabel('幅度(dB)');grid on;

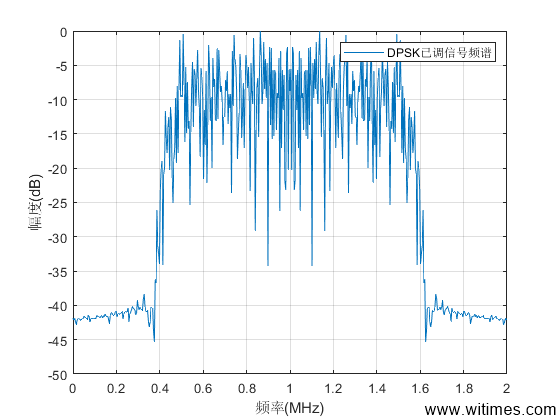

最終繪制的DPSK已調信號頻譜如下圖,可見,信號頻譜被限制在1.25MHz左右,與預期是相符的。

這段代碼用于在FPGA中生成偽隨機數作為源,事實上FPGA中不可能真的生成隨機數,只是這些數的周期很長而已。有一點需要注意的是,用于DPSK調制的數字序列必須具有隨機性,否則頻譜會出現單獨的峰。偽隨機數模塊的時鐘速率是2MHz。代碼如下:

在我看來,星座映射就是個簡單的組合邏輯,但是聽著很高大上,所以教科書里面都這樣寫,在這個系列的第一篇文章中,已經說明了要采用-1 1這樣的序列來替代0 1序列,所以需要把FPGA生成的隨機的0 1序列變為隨機的-1 1序列,在這里,我采用通常的二進制補碼來表示-1,以便與其他模塊對接。星座映射的代碼如下:

module code_convert(

input code_convert_clk,

input code_convert_din,

input code_convert_rst,

output [7:0] dout

);

reg pre_code;

reg pre_code_temp;

reg [7:0] code_convert_dout;

always @(posedge code_convert_clk)

begin

if(code_convert_rst==0)

pre_code_temp <= code_convert_din;

else

begin

if (code_convert_din == pre_code_temp)

begin

code_convert_dout=8'b11111111; //Change to bi-polar code -1.

pre_code_temp <= 1'b0;

end

else

begin

code_convert_dout=8'b00000001; //Change to bi-polar code +1.

pre_code_temp <= 1'b1;

end

end

end

assign dout=code_convert_dout;

endmodule

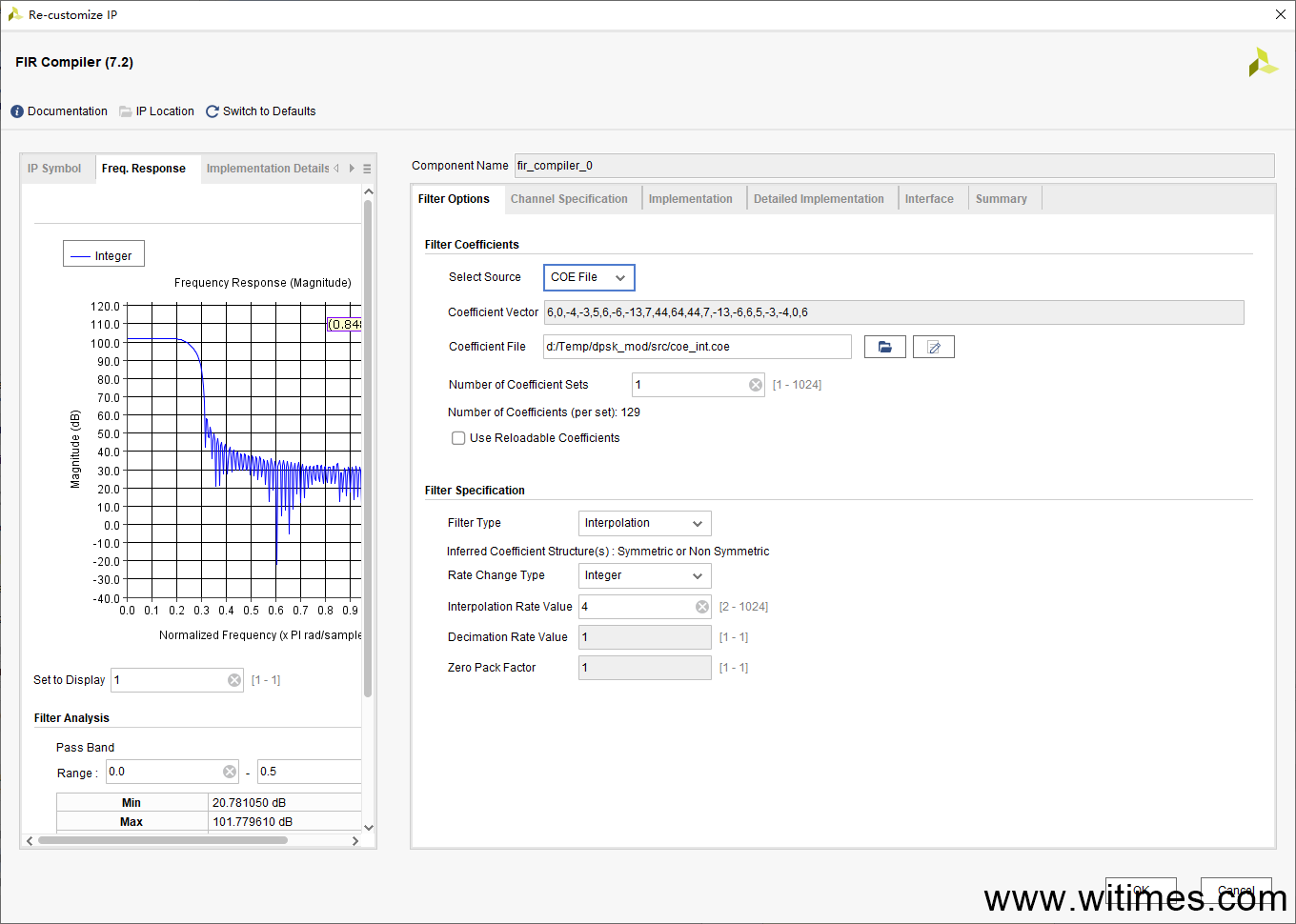

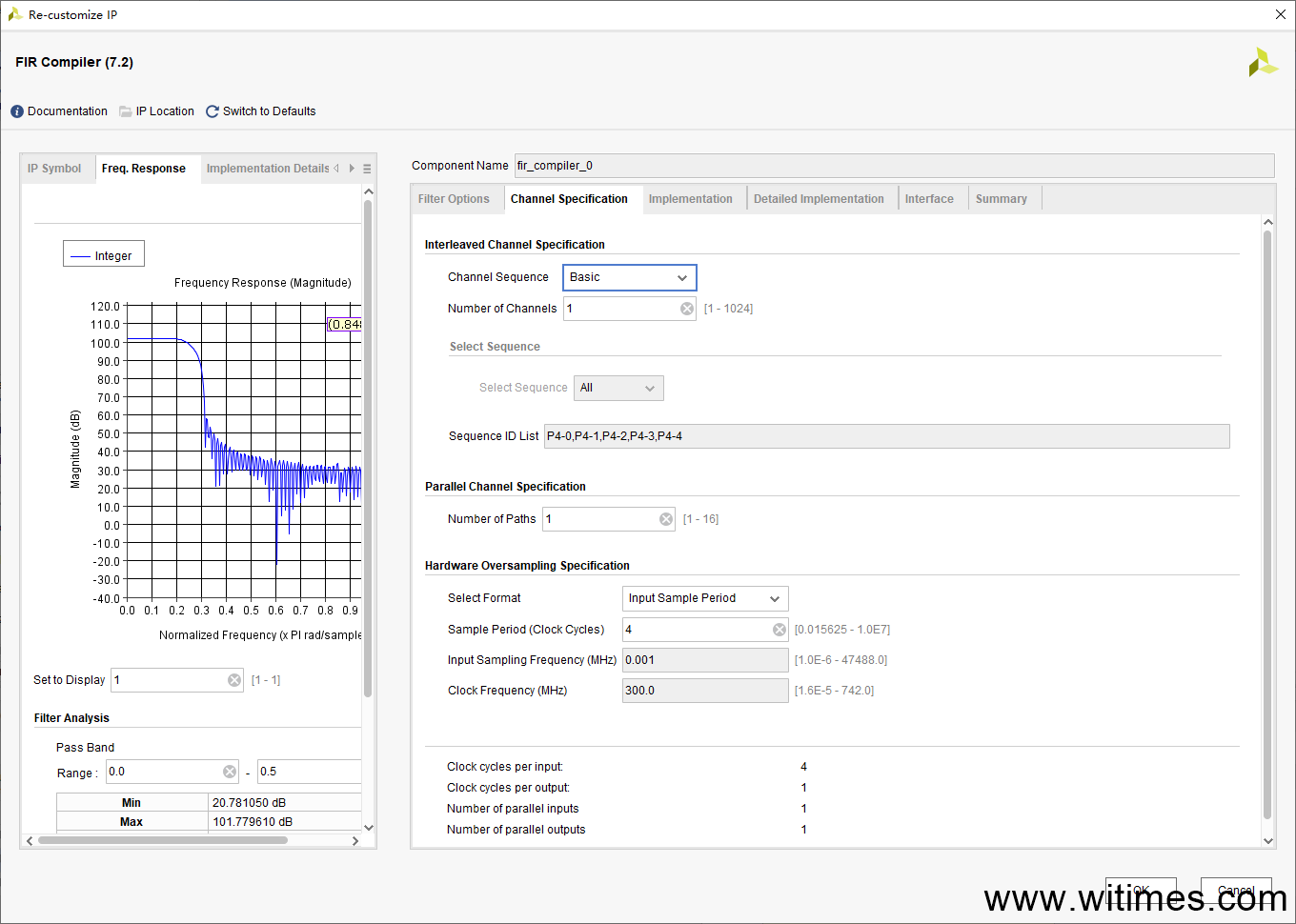

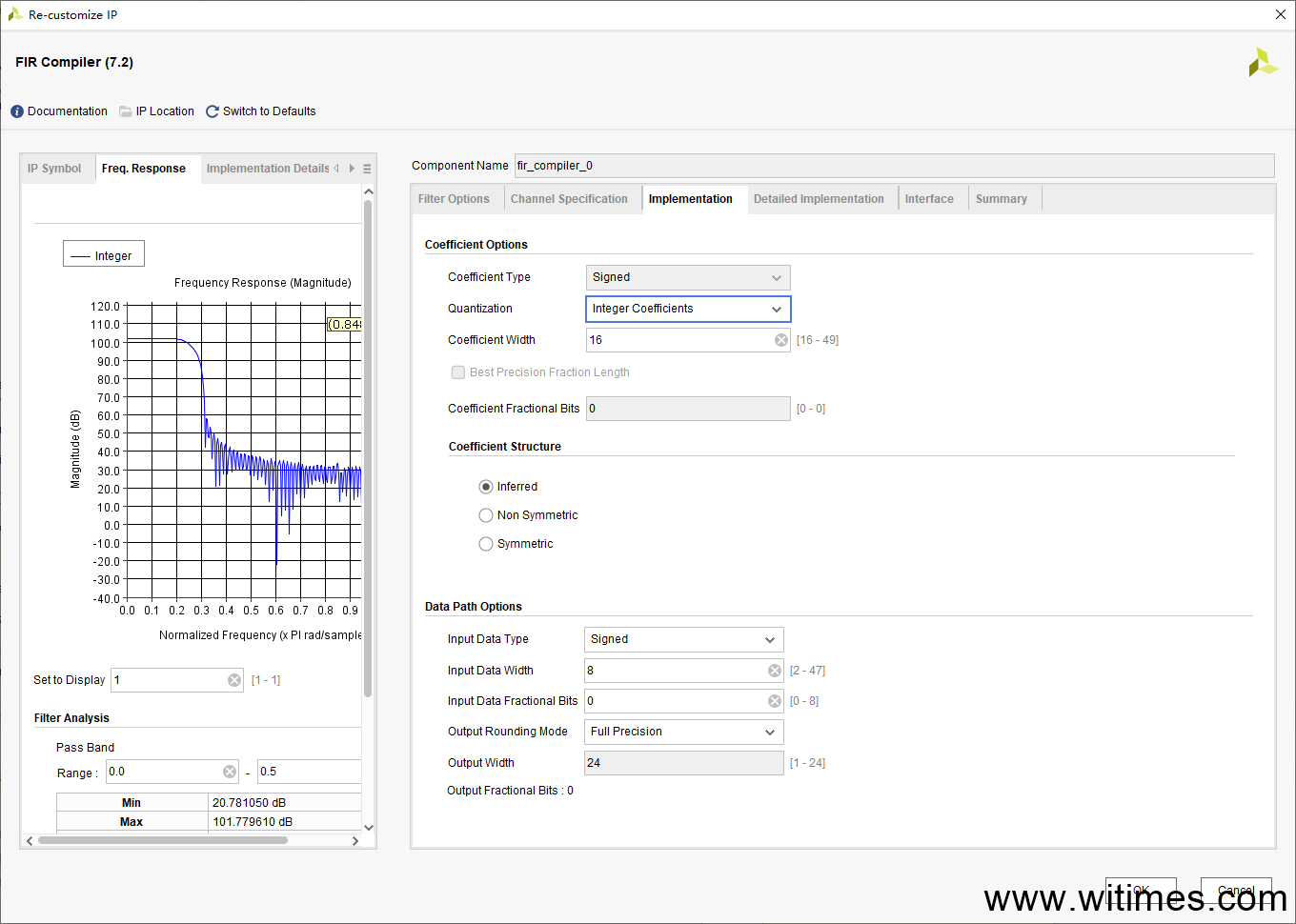

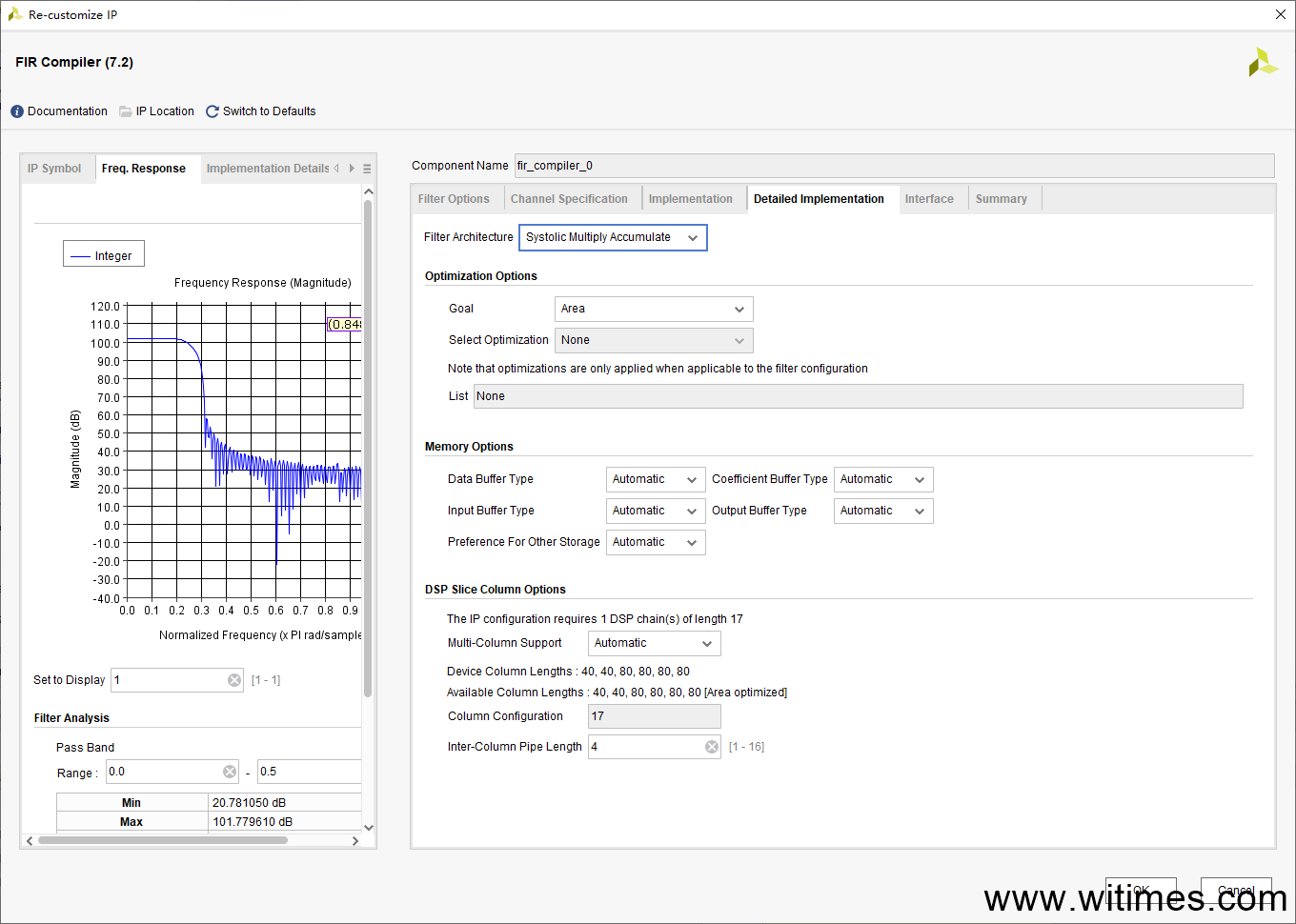

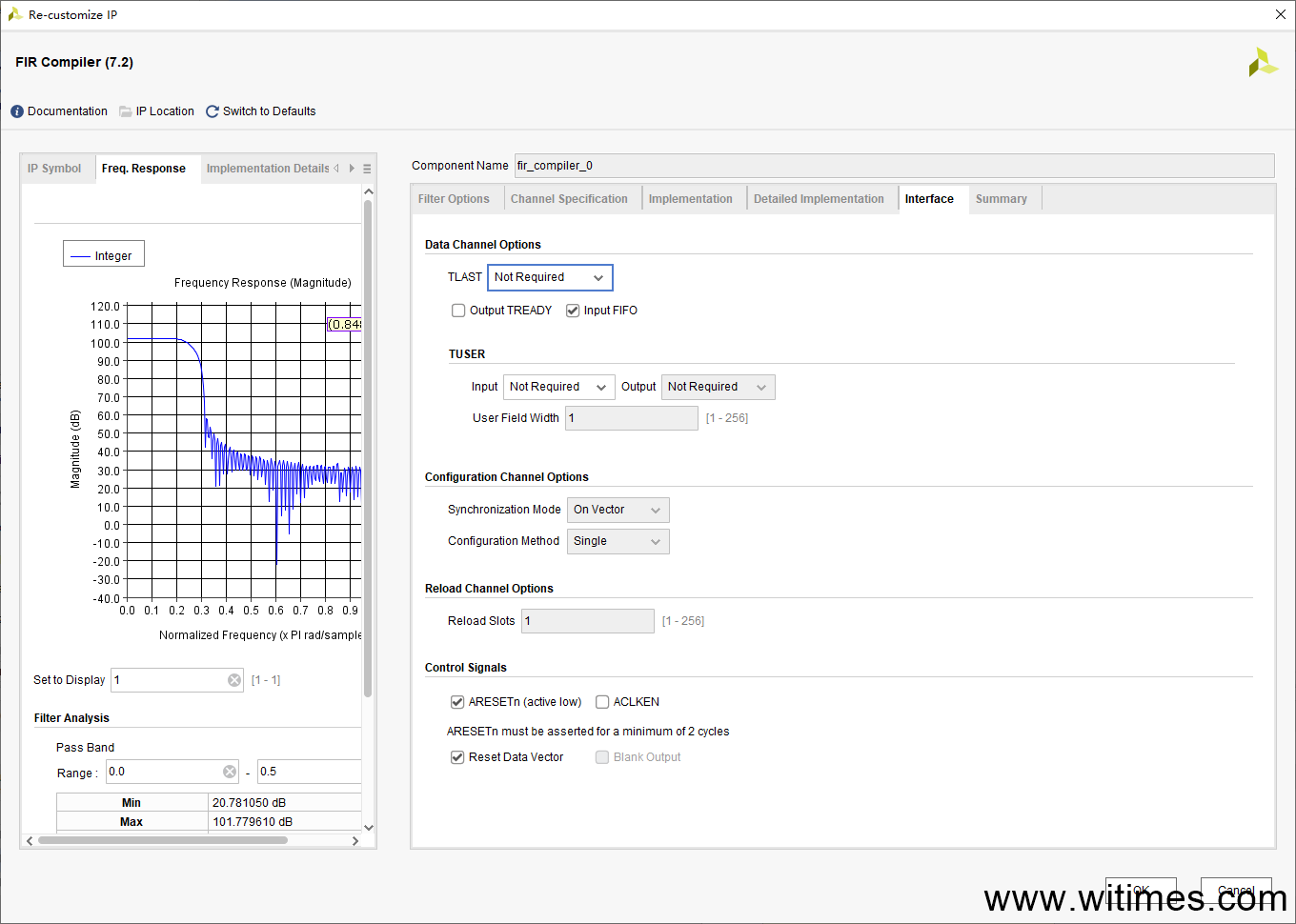

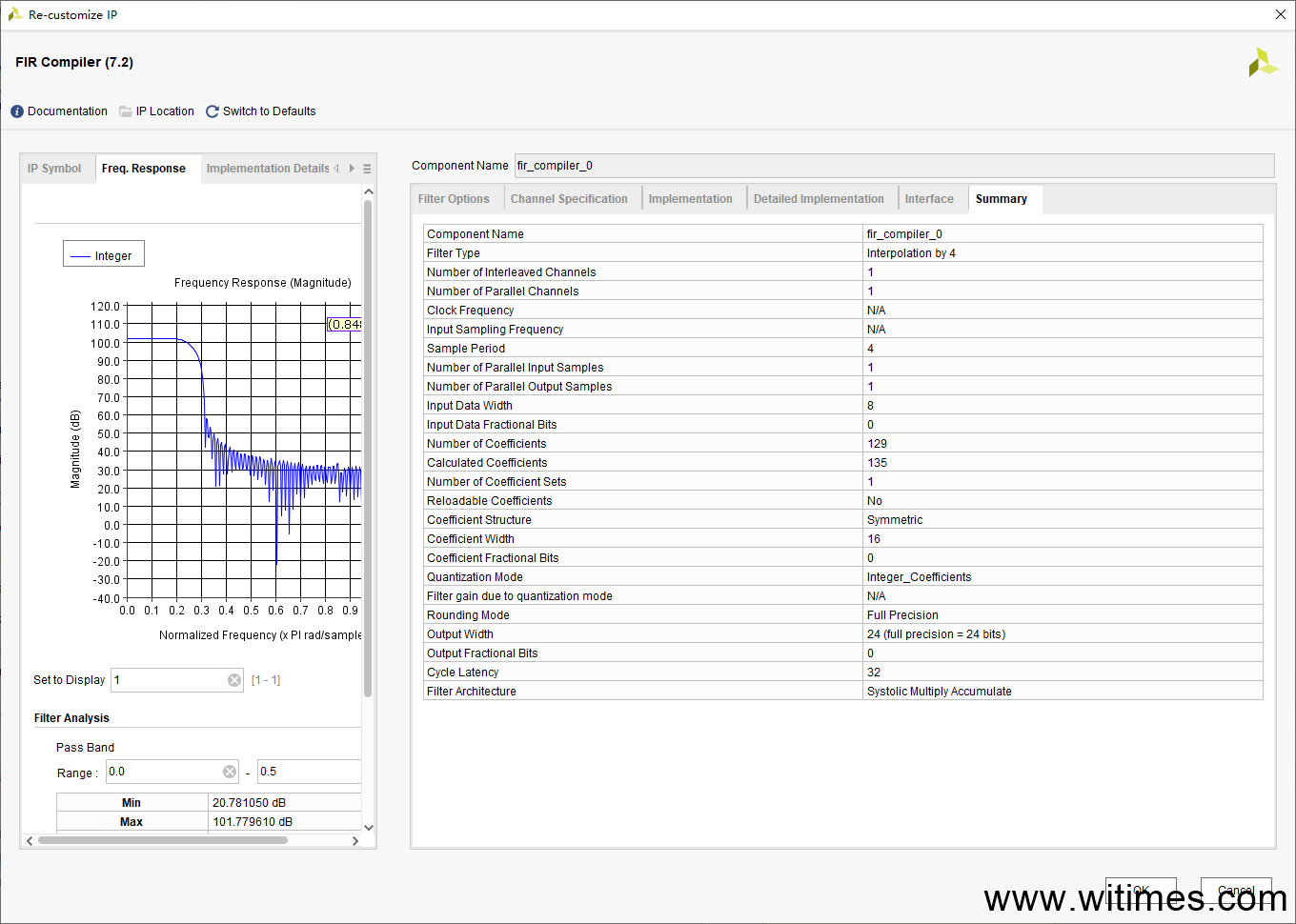

這部分我直接用了Vivado的FIR IP核,將其配置為4倍內插方式,并使用上一篇文章中生成的濾波器系數,如下圖

這里我們再來看看數據速率的變化。原始數字序列的速率是2Mbps,經過星座映射后仍是2Mbps,但是經過FIR的4倍內插之后,速率變為了8Mbps,由于FIR內插的都是0,在這期間不能讓FIR的輸入端獲得有效數據,于是這里有個很重要的操作,就是保證FIR的輸入端在8MHz時鐘的驅動下,每4個時鐘周期使能一次FIR的m_tvalid信號,這樣才能保證結果的正確性。代碼如下:

reg [1:0] axis_cnt=0;

always @(posedge clk_8m)

begin

if(!Hard_rstn)

axis_cnt <= 'd0;

else if(s_data_tvalid)

axis_cnt <= axis_cnt + 1'b1;

end

wire m_tvalid;

assign m_tvalid = (s_data_tvalid==1'b1) && (axis_cnt==3'd3);

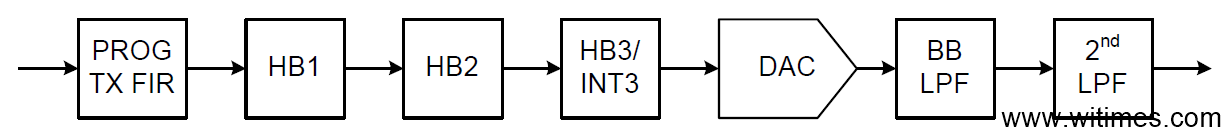

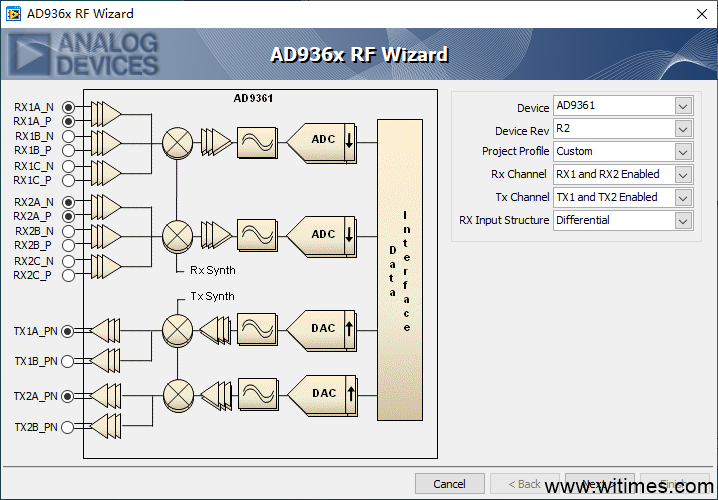

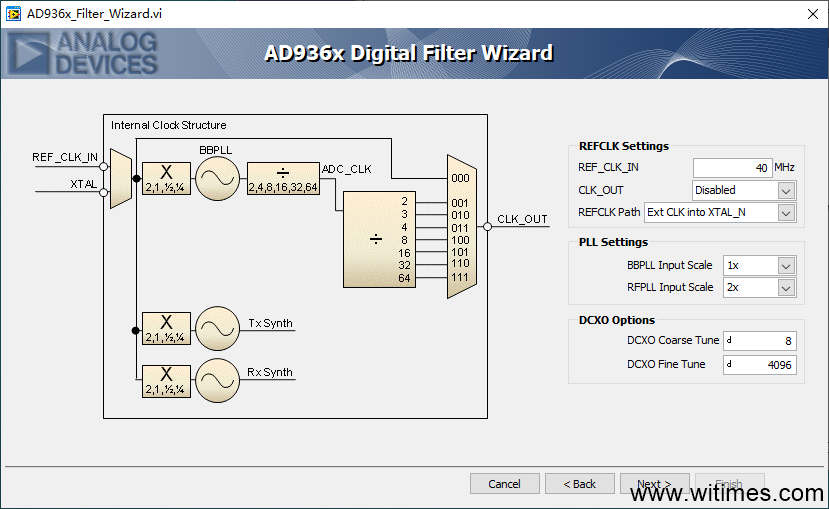

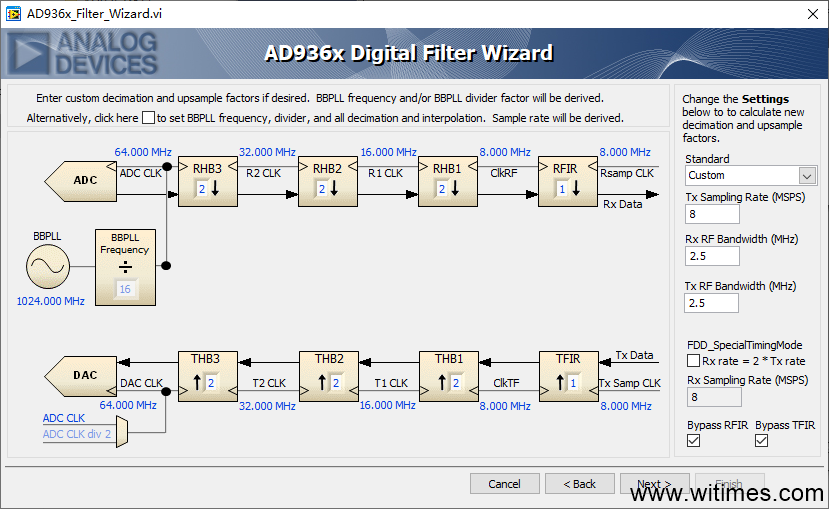

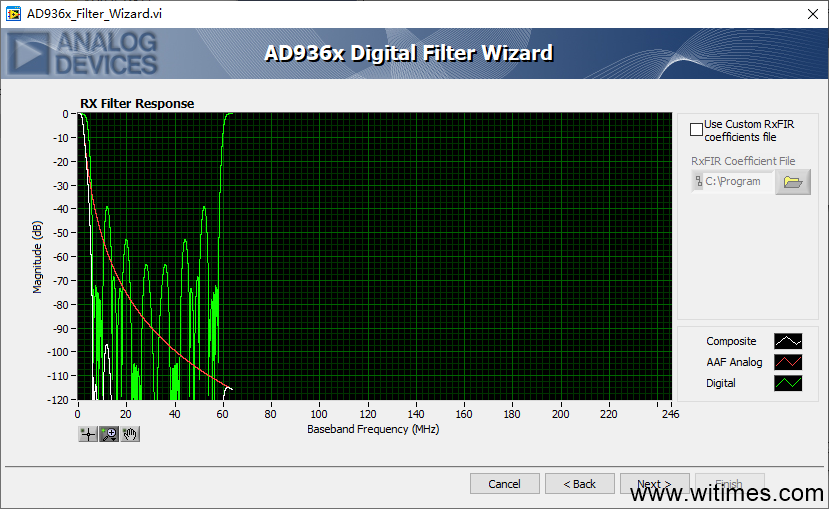

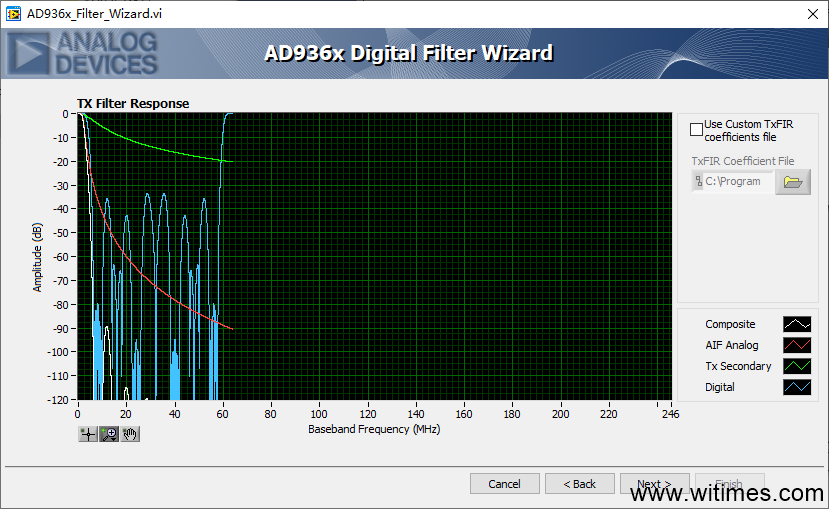

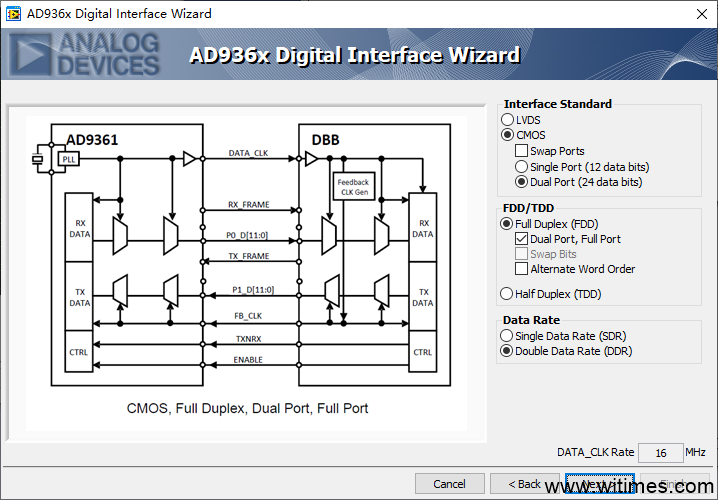

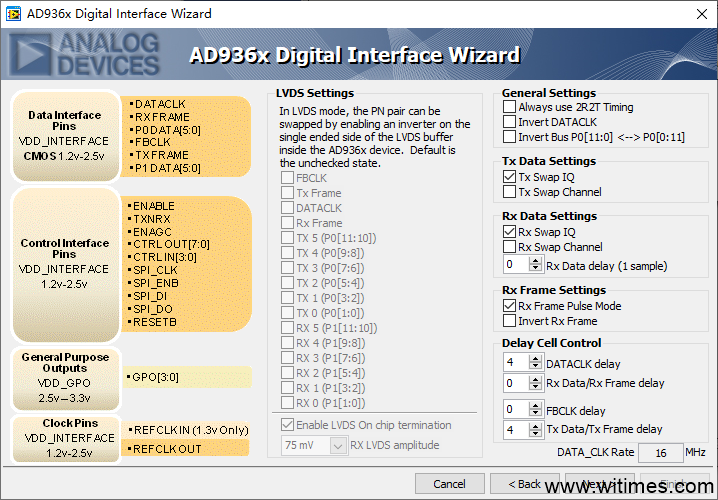

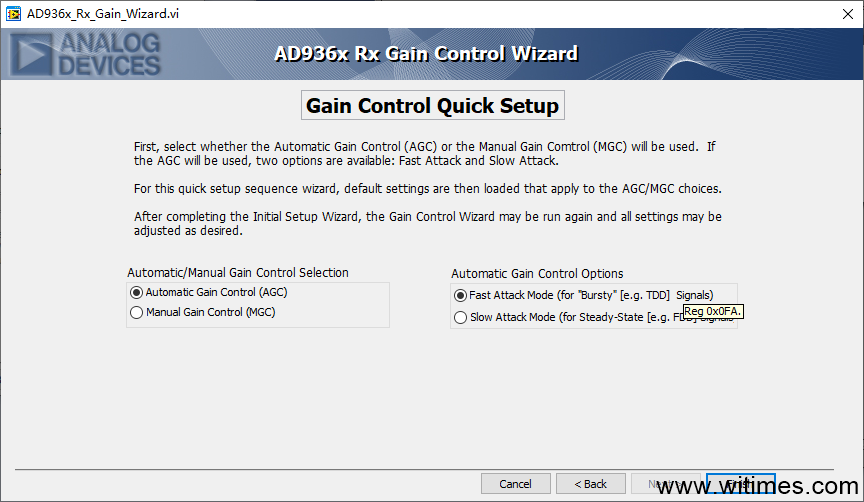

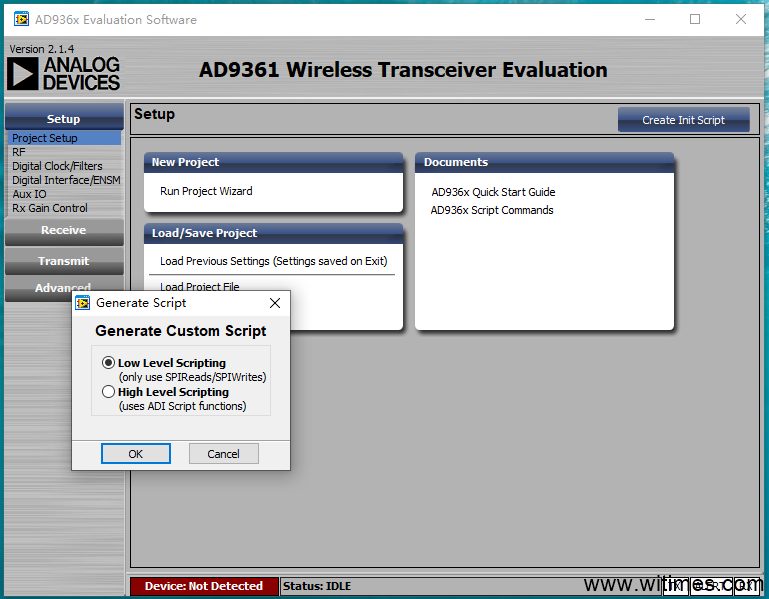

早在2016年的時候一個朋友就跟我說AD9361內部有2000多個寄存器,看著頭疼,在我這次的軟件無線電工程實踐過程中,也同樣感覺到很頭疼,好在ADI官方有個小軟件,可以圖形化操作,用起來很方便。本項目配置過程重點要考慮AD9361內部的濾波器,如下圖。

AD9361內部集成了4個數字濾波器包括1個可編程FIR濾波器和3個半帶濾波器,AD9361內部還集成了2個可編程的模擬濾波器。我本想把前面生成的系數寫入AD9361的寄存器,這樣可以減少占用的FPGA資源,可是AD9361的FIR濾波器只能寫入128個系數,而我用Matlab生成的系數確是129個,實在沒想明白怎么辦。所以在我的配置中,bypass掉了AD9361的FIR濾波器,后面的3個半帶濾波器則正常使用,2個模擬濾波器也正常配置。配置過程如下:

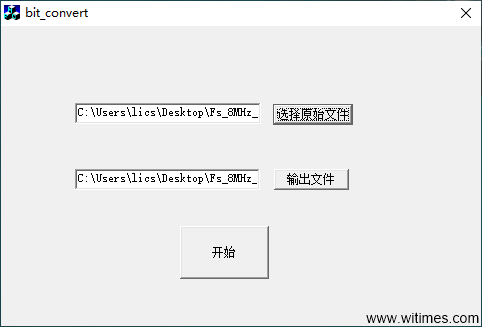

生成初始化腳本后,使用一個convert.exe的小軟件,將腳本轉換為verilog代碼,如下圖

本項目中使用FPGA模擬SPI接口直接對進行AD9361配置,用了別人編寫好的代碼^_^,我只是把其中的寄存器參數替換成了剛剛生成的。ADI公司還提供了no-OS代碼,可以移植到單片機上或者FPGA的軟核,這里就不展開敘述了。

還有二點值得注意的是:FIR的輸出直接給到AD9361,位寬是不匹配的,我做了個簡單粗暴的操作,直接把FIR的高12位輸出給到AD9361,畢竟低位數據影響不大;DPSK方式,IQ支路只用一路就好,我的代碼中I路對應FIR輸出的高12位,Q路始終為0。代碼如下:

assign tx_i_ch1=srrc_out[16:5];

assign tx_q_ch1=12'b0;

assign tx_i_ch2=srrc_out[16:5];

assign tx_q_ch2=12'b0;

至此,已經完成了DPSK調制的所有功能模塊,如下圖:

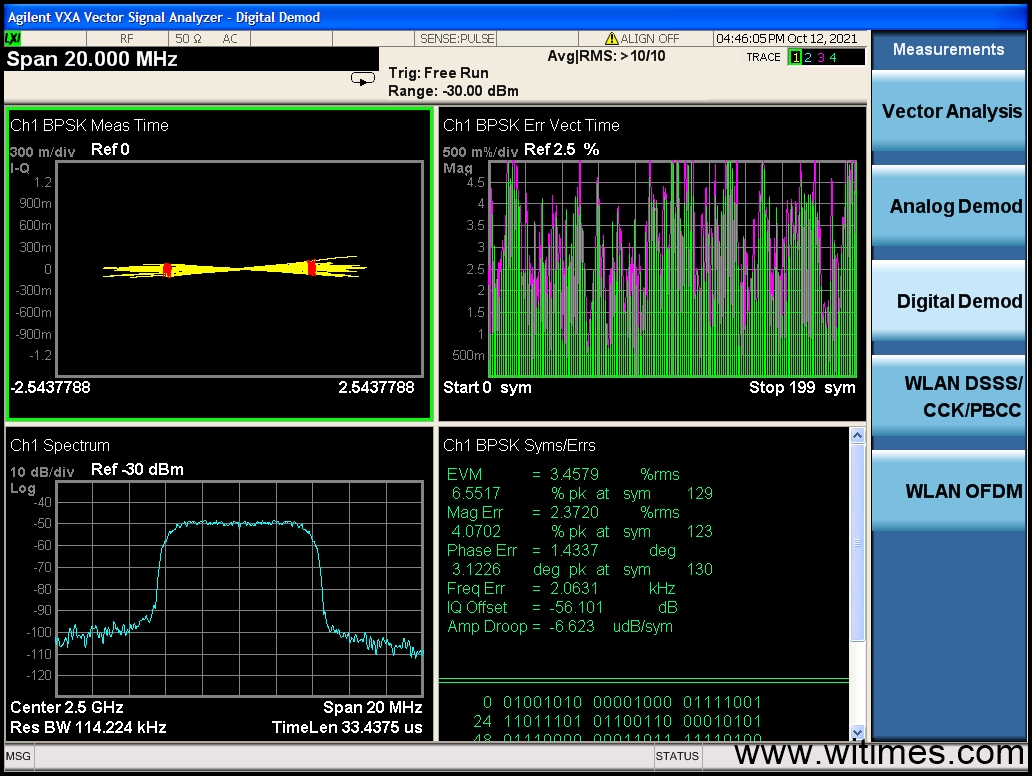

使用Vivado編譯完整工程,將最終得到的bitstream文件寫入FPGA,就在頻譜儀上看到了預期的波形,這是最讓人激動的時刻,如下圖。

至此,關于DPSK調制的完整實驗都已經完成,我又嘗試了幾種不同的采樣率和信道帶寬,都能與預期的波形相符。回想這些年的研發經歷,這次試驗是我唯一能夠了解到底層機制的一次,甚至可以知道每一個bit是怎么來的,也是我第一次把數學與工程實踐相結合,領略到數學之美的同時也感受到了數字基帶開發的樂趣:可計算、可仿真、可實際驗證。其實這3篇文章提煉出來的都是我在學習實踐過程中總結出來的要點,我自己深入學習差不多有半年的時間才搞出來DPSK的波形,而且這僅僅是發射部分,有個高手說接收比發射復雜10倍,未來還有很長的路要走。

下一篇: PLC、DCS、FCS三大控

上一篇: 5.8GHz大功率無線網橋