“人如其食”是一個(gè)常見說法,建議您仔細(xì)選擇食物,因?yàn)樗鼤?huì)直接影響我們的健康和福祉。

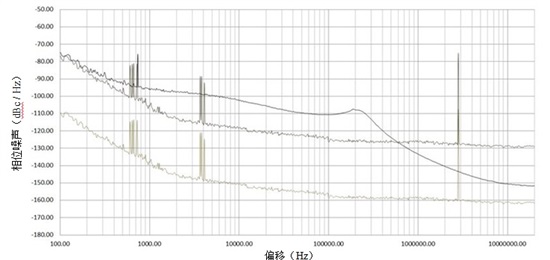

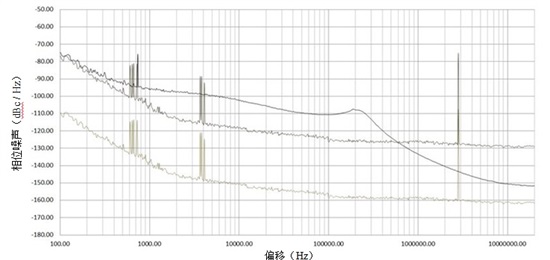

雖然并非精確的比較,但這一概念適用的前提是您將輸入?yún)⒖夹盘?hào)視為食物,由鎖相環(huán)(PLL)/合成器攝入,這會(huì)影響PLL/合成器的性能,可在圖1所示的輸出相位噪聲中可見一斑。在本博文中,我將提供一些實(shí)際示例來說明什么是良好的輸入?yún)⒖迹涣驾斎雲(yún)⒖紩?huì)造成何種損壞,以及如何分析給定的輸入?yún)⒖肌?/p>

圖1:輸入?yún)⒖荚肼曇渤艘?/strong>PLL

往后倒推一步,當(dāng)與壓控振蕩器(VCO)配對(duì)時(shí),PLL成為可鎖定到低頻信號(hào)(來自穩(wěn)定晶體振蕩器的10MHz)的控制環(huán)系統(tǒng),并將其乘以更高的頻率(LMX2592可徑直乘以9.8GHz)。

示例1

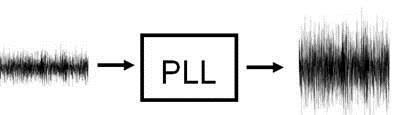

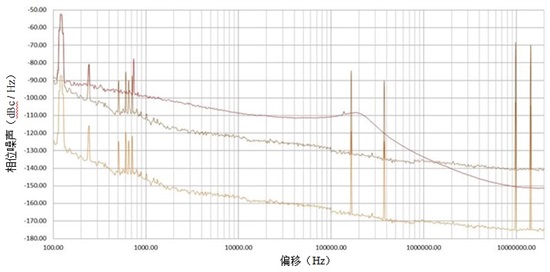

圖2所示為單邊帶相位噪聲圖。橙色線是100MHz輸入?yún)⒖夹盘?hào),它使用非常低的相位噪聲晶振作為輸入?yún)⒖肌1纠械腖MX2582合成器將100MHz倍頻到5,160.96MHz。如此以來,輸入?yún)⒖荚肼曇惨訹20×LOG(5,160.96 / 100)= 34.25dB]的系統(tǒng)成比例增大。棕色線顯示放大結(jié)果(以數(shù)學(xué)方式調(diào)整)。紅色線表示5160.96MHz時(shí)LMX2582的輸出。

圖2:低相位噪聲100MHz輸入?yún)⒖己?/strong>5160.96MHz LMX2582輸出

使用類似于圖2中的一個(gè)輸入?yún)⒖硷@示合成器的性能,因?yàn)檩斎雲(yún)⒖枷辔辉肼曌銐虻汀W⒁猓P(guān)鍵區(qū)域在環(huán)路帶寬(?300kHz偏移)下,因?yàn)槌^該偏移頻率,輸入?yún)⒖荚肼曇脖贿^濾,并且將以與紅線(在該示例中未示出)相同的方式下降。

還要注意輸入?yún)⒖荚诩s120Hz的峰值。這直接影響輸出相位噪聲。您可能已在此處看到危險(xiǎn)。若噪聲在較低偏移處在某處耦合到輸入?yún)⒖荚粗校敲此赡軗p壞合成器相位噪聲。

示例2

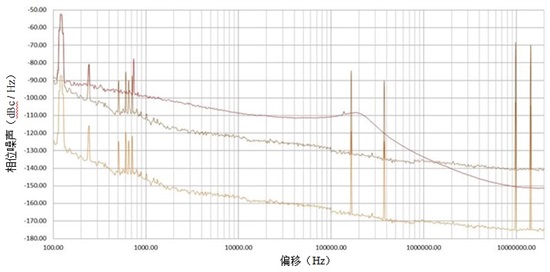

圖3考慮了另一個(gè)輸入?yún)⒖迹@次是一個(gè)122.88MHz的晶體振蕩器。輸出頻率仍為5,160.96MHz。此時(shí),輸入?yún)⒖荚肼暟碵20 x LOG(5,160.96 / 122.88)= 32.46dB]的系數(shù)進(jìn)行縮放。查看相位噪聲部分2kHz偏移及以下,并將其與圖2的輸出相位噪聲進(jìn)行比較;您可看到,這個(gè)更高的輸入?yún)⒖荚肼曍暙I(xiàn)量直接提高了來自合成器的輸出相位噪聲。為了從LMX2582實(shí)現(xiàn)最佳性能,您還必須為它提供一個(gè)足夠好的輸入?yún)⒖肌2⑶伊私庠肼暼绾慰s放和貢獻(xiàn)有助于通過其基本相位噪聲電平來選擇輸入?yún)⒖夹盘?hào)。

圖3:一個(gè)122.88MHz輸入?yún)⒖己?/strong>5160.96MHz LMX2582輸出

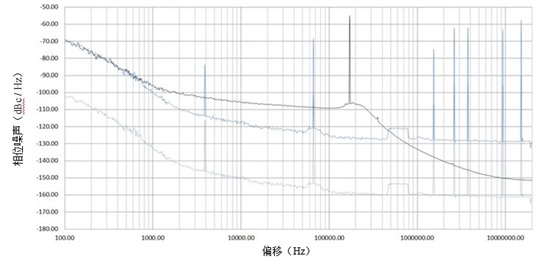

示例3

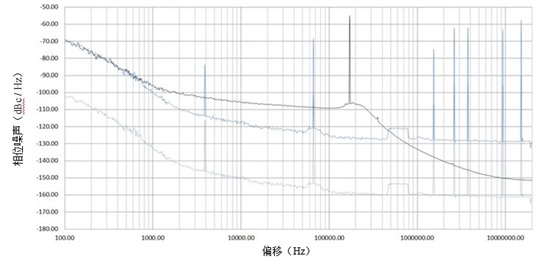

圖4探討了另一種情況。本例還使用了一個(gè)122.88MHz的晶體振蕩器,但這次是從振動(dòng)產(chǎn)生相位噪聲的影響。當(dāng)您點(diǎn)擊靠近振蕩器的手指時(shí),會(huì)出現(xiàn)圖4中的那些尖峰。這是在某些基于晶體的振蕩器中的已知行為。它的損壞方式與不良相位噪聲相同,但若您只是將其留在工作臺(tái)上并進(jìn)行測(cè)量,您可能不會(huì)了解它。這表明在選擇輸入?yún)⒖紩r(shí),重要的是不僅要了解設(shè)備的基本相位噪聲,還要了解其對(duì)振動(dòng)、老化、溫度變化、對(duì)電源噪聲的彈性和許多其它影響的響應(yīng)。考慮到這一點(diǎn),可以幫助選擇部件并調(diào)試整個(gè)信號(hào)鏈。

圖4:噪聲122.88MHz輸入?yún)⒖己?/strong>5160.96MHz LMX2582輸出

要了解這在示例設(shè)計(jì)中如何工作,請(qǐng)查看我們從降壓轉(zhuǎn)換器工作的9.8 GHz RF高性能合成器參考設(shè)計(jì)。

參考表

作為指導(dǎo),觀察到計(jì)算的縮放輸入?yún)⒖荚肼暤挠绊懯怯袔椭摹T诒?中,您可看到(如預(yù)期的那樣)若縮放的輸入?yún)⒖枷辔辉肼暸cPLL相位噪聲(表1中的0dB)相同,則您將獲得3dB的噪聲增量,因?yàn)槟龑⒃肼暳考颖丁M瑯樱裟M(jìn)一步降低輸入?yún)⒖嫉南辔辉肼曤娖剑敲磳?duì)相位噪聲的影響越來越小。

表1:來自縮放輸入?yún)⒖枷辔辉肼暤南辔辉肼?/strong>

通過這些示例,我希望我已展示一個(gè)良好的輸入?yún)⒖紝?duì)于從合成器獲得最佳性能的重要性。不良輸入?yún)⒖疾粌H是相位噪聲電平過高,且是更易受外部影響(振動(dòng),老化,溫度,電源)的參考。憑借這些信息,您在設(shè)計(jì)合成器的輸入?yún)⒖紩r(shí)應(yīng)該會(huì)獲得更好的理解和更多的想法。有關(guān)其他信息或有任何疑問,請(qǐng)?jiān)L問德州儀器在線支持社區(qū)高性能RF調(diào)制器、PLL和VCO論壇。

其他信息